안녕하세요. 취업한 공대누나입니다.

지난 시간에는 래치의 개념과 SR 래치에 대해 알아보았습니다.

오늘은 래치의 또 다른 종류인 D 래치에 대해 알아보았습니다.

Latch의 개념을 잘 모르는 분들은 아래 포스팅을 참고해주세요!

2022.06.07 - [전자 공학/논리회로] - SR 래치(Latch)란?

SR 래치(Latch)란?

②안녕하세요. 취업한 공대누나입니다. 오늘은 래치의 개념을 알아보고, 특히 SR래치에 대해서 알아보도록 하겠습니다. 1. SR래치란? 래치란?! 래치(Latch)는 순차회로에서 한 비트의 정보를 저장하

gdnn.tistory.com

1. D래치의 동작

Gated D Latch, 게이트형 D 래치 라고도 합니다.

SR 래치에서 S는 Set, R은 Reset을 의미했습니다.

간단하게 D래치라고 말하도록 하겠습니다.

그렇다면 D래치에서 D는 무엇을 의미할까요? 바로 Data입니다.

D래치의 입력은 D와 Gate(Enable) 핀입니다.

그리고 출력은 Q와 Q'입니다.

동작은 Gate가 High 신호일 때 D 값이 출력됩니다.

그리고 Gate가 Low이면 이전 값을 유지하게 됩니다.

특성표로 보게되면 아래와 같습니다.

| Enable | D | Q | Q' |

| 0 | X | 이전 값 | 이전 값 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

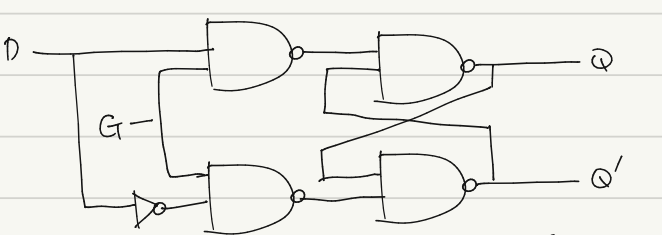

2. D래치 구성

회로 구성은 위와 같습니다.

동작을 살펴보기 전 NAND Gate의 특징을 한 번 보고 가도록 하겠습니다.

하나의 Input이 0일 경우 다른 Input과는 상관없이 결과는 1이됩니다.

하나의 Input이 1일 경우에는 다른 Input과 반대되는 값이 출력으로 나오게 됩니다.

이 특징을 기억하고 동작을 보면 쉽습니다.

1) G = 0, D= 0

G가 0이면 왼쪽의 NAND 게이트들의 출력은 무조건 1이됩니다.

그러면 오른쪽 NAND 게이트들의 한쪽 Input이 1이 되겠지요.

그래서 나머지 Input의 반대 값을 출력하게 되면 Q와 Q'이 나오게 됩니다.

즉 Gate가 Low이면 이전 값을 유지하는 것을 알 수 있습니다.

2) G=1, D=0

왼쪽의 NAND Gate를 보게 되면 G=1이므로 나머지 Input의 반대값이 출력되게 됩니다.

그래서 위의 Nand의 출력은 1, 아래쪽 Nand 게이트의 출력은 0이 됩니다.

그리고 이 때, 오른쪽 아래 NAND Gate를 보게 될 경우 Input이 0이므로 출력은 무조건 1이됩니다.

그래서 Q' = 1이 됩니다. 그리고 이 값이 오른쪽 위의 Nand Gate의 Input이 되므로 Q=0이 됩니다.

즉 D값이 그대로 Q로 출력되는 것을 알 수 있습니다.

회로가 대칭이기 때문에 G=0, D=1인 경우와 G=1, D =1인 경우는 따지지 않았습니다.

천천히 해보시면 쉽습니다.

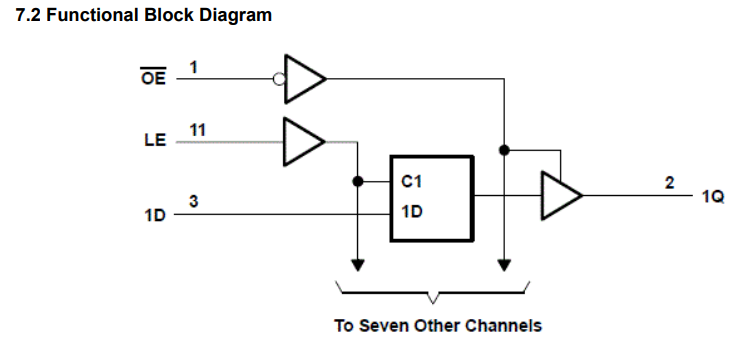

3. D Latch 데이터시트 보기

D Latch 소자의 데이터시트를 한 번 보도록 하겠습니다.

Mouser에서 검색해보았습니다.

부품 이름은 TI사의 CD74HC373E입니다.

Block Diagram을 보니 우리가 공부한 것과는 조금 다른 느낌입니다.

Input이 3개인 것 같네요.

설명을 한 번 보도록 하겠습니다.

OE Pin은 래치의 내부 동작에는 영향을 미치지 않는다고 되어있습니다.

동작만을 보면 OE핀의 경우 Low로 해놓은 상태에서 사용하면 됩니다.

OE를 제외하고 LE는 Gate Pin이라고 생각하면 우리가 알고 있는 동작과 같습니다.

'전자 공학 > 논리회로' 카테고리의 다른 글

| 보수란? - 1의 보수, 2의 보수 (1) | 2022.06.15 |

|---|---|

| SR 래치(Latch)란? (0) | 2022.06.07 |