안녕하세요. 취업한 공대누나입니다.

오늘은 CMOS 소자에 대해 알아보도록 하겠습니다.

1. CMOS란?

Complementary metal-oxide-semiconductor의 약자로 상보적 금속 산화물 반도체를 뜻합니다.

일반적으로 '씨모스'라고 읽습니다.

주로 마이크로프로세서나 SRAM, 이미지 센서 등의 집적회로를 구성하는데 사용되고 있습니다.

CMOS는 MOSFET 소자로서 PMOS와 NMOS가 상보적 대칭으로 사용되는 공정을 의미합니다.

PMOS와 NMOS의 단점을 상쇄시키고, 장점만을 활용하여 좋은 특성을 극대화시킬 수 있습니다.

그렇다면 NMOS와 PMOS의 장점과 단점은 무엇일까요?

<NMOS의 장점과 단점>

증가형 NMOS의 경우 Gate에 +전압을 인가하게 될 경우 ON이 됩니다.

이 때, 소스 단자로 들어오는 입력 신호의 Low level은 손실 없이 잘 전달되어 드레인 단자로 출력되게 됩니다.

하지만, High Level은 Vth의 손실로 인하여 Vth의 값을 차감한 값 (Vdd-Vth)으로 출력되게 됩니다.

<PMOS의 장점과 단점>

증가형 PMOS의 경우에는 Gate에 - 전압을 인가하게 될 경우 ON이 됩니다.

소스 단자로 신호를 입력하면 High Level은 손실 없이 잘 전달되어 출력되게 됩니다.

하지만 Low Level인 경우 Vth의 손실로 인하여 Low level 전압 + Vth의 값으로 출력되기 됩니다.

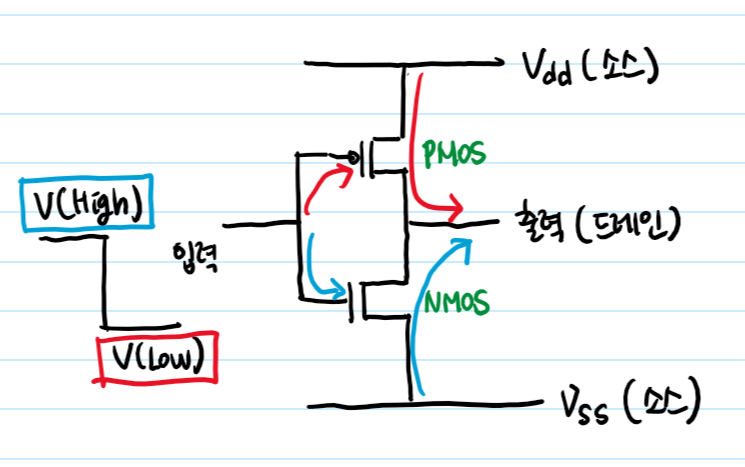

CMOS는 주로 인버터에 많이 사용되는데요.

인버터를 예로 들어보도록 하겠습니다.

입력으로 High 전압이 인가될 경우

NMOS만 쇼트가 되게 됩니다. 그래서 Source와 Drain이 연결되므로 Vss가 출력되게 됩니다.

이 때 Vss에 GND를 연결시키게 되면 Low level이 출력되게 되겠지요.

입력으로 Low 전압이 인가될 경우

이번에는 PMOS만 쇼트가 되게 됩니다. 마찬가지로 PMOS의 Source와 Drain이 연결되므로 Vdd가 출력되게 됩니다.

(제가 그림에 Vdd라고 잘못 적어놨는데, 실제로는 Vss가 맞습니다.)

여기서 Vdd에 5V 혹은 3.3V 등의 High 전압을 연결시키게 되면 High Level이 출력되게 됩니다.

예시를 든 것처럼 NMOS일 경우 Low level을 전달하고, PMOS일 경우 High Level을 전달하도록 회로를 꾸미게 되면

위의 단점에서 설명한 Loss없이 시그널이 출력되게 됩니다.

CMOS는 동작 속도가 빠른 편은 아니지만 로스가 적기도 하고

두 소자가 동시에 ON이 되는 일이 없으므로 소비 전력이 적다는 장점이 있습니다.

이러한 것을 보면 과학자?들은 정말 대단하다는 생각이 듭니다.

NMOS와 PMOS를 어떻게 결합할 생각을 했는지 아이디어가 놀랍고 부럽습니다.

저런 아이디어가 있다면 먹고 살 걱정 없는 부자가 될 수 있을텐데요.

다음 시간에도 생각나는 소자가 있으면 포스팅 해보도록 하겠습니다.

'전자 공학 > 소자' 카테고리의 다른 글

| 이더넷 스위치 IC (1) | 2021.09.24 |

|---|---|

| 사이리스터, SCR, 트라이악이란? (1) | 2021.02.17 |

| [IGBT] IGBT란? (2) | 2020.11.11 |

| [포토커플러] 포토커플러란? (2) | 2020.11.06 |

| [FPGA] FPGA란 무엇인가? (5) | 2020.10.27 |